“Is there still plenty of room at the bottom?”ou

Oů va la microélectronique ?

Par Claude Weisbuch, Genewave et Laboratoire de la Matičre Condensée, Ecole Polytechnique, Palaiseau

Michel Brillouët, CEA-LETI, Grenoble

Introduction

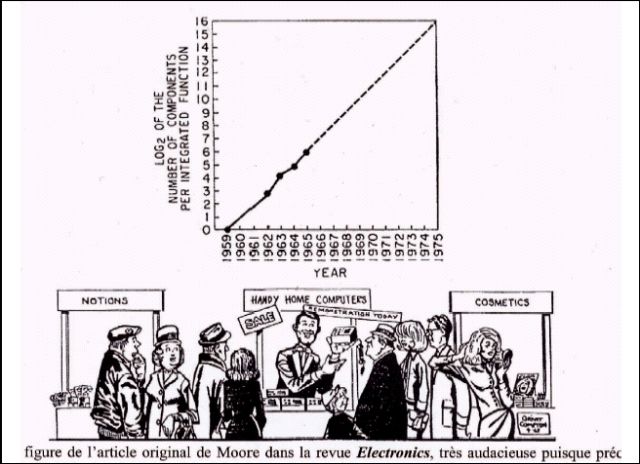

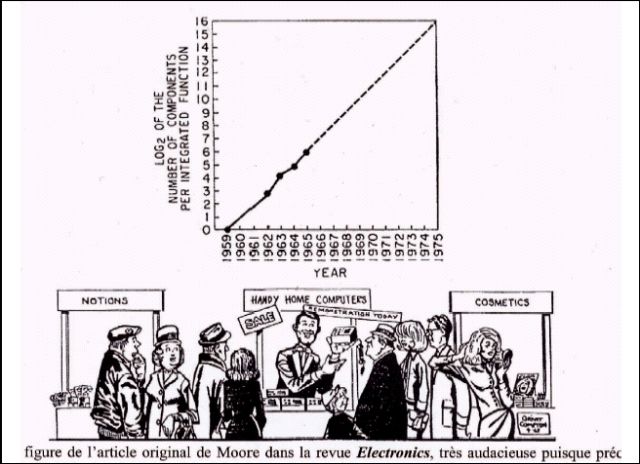

Gordon Moore, dans un article visionnaire

d’Electronics1 (Figure 1),

annonçait en 1965 le

doublement tous les ans du nombre de transistors

dans les circuits intégrés, prédisant le passage de

60 transistors ŕ l’époque ŕ 60 000 en 1975, objectif

effectivement atteint. Plus récemment, un doublement

tous les 18 mois environ est observé, permettant

de dépasser le cap du milliard de transistors

sur la puce en l’an 2000. Cette vision se décline

aujourd’hui par une feuille de route

(l’International Technology Roadmap for

Semiconductors, la roadmap de l’ITRS), consensus

international sur les moyens ŕ développer pour

continuer ŕ progresser selon cette « loi de Moore ».

Quatre ans plus tard, Richard Feynman, dans sa

conférence visionnaire, célčbre aujourd’hui, quelque

peu ignorée pendant une vingtaine d’années,

“There’s plenty of room at the bottom”2 , jetait les

fondements des nanotechnologies en imaginant,

bien avant l’avčnement du microscope ŕ force atomique,

la manipulation d’objets au niveau de l’atome3 . Cette perspective permet aujourd’hui de

repenser le composant électronique ŕ partir d’éléments nanométriques assemblés, présentés souvent

comme le futur de la microélectronique.

Qu’en est-il vraiment ?

Aprčs avoir discuté les perspectives

actuelles de la microélectronique au moment oů

elle entre dans le domaine nanométrique, nous

explorerons les composants dits émergents souvent

présentés comme une alternative au CMOS.

Nous nous attarderons enfin sur quelques maničres

d’interfacer les circuits avec le monde réel, un

domaine connexe en pleine expansion et oů la

miniaturisation et les nanotechnologies ont un

grand rôle ŕ jouer.

Evolutions de la microélectronique : la feuille de

route microélectronique et ses bases physiques

Qu’est-ce qu’un « bon » transistor ?

Le bon fonctionnement des circuits électroniques

complexes suppose l’intégration de nombreux

composants, une manipulation de l’information sans dégradation, des taux d’erreurs par composant

réduits, des possibilités de corriger les

erreurs restantes, une bonne fiabilité d’un ensemble

de milliards de composants élémentaires, des

taux de défauts ŕ la fabrication extręmement faibles,

etc.. Cela exige que le composant électronique actif

de base soit "sain". Un bon composant électronique

pour la trčs grande intégration repose sur un certain

nombre de principes qu’il faut rappeler4 lorsque l’on

veut étudier les évolutions et les mutations de la

miniaturisation.

La non dégradation du signal - Un signal

porteur d’information a tendance ŕ se dégrader en

se propageant : le transistor a un rôle fondamental

dans la régénération du signal digital. Son gain et

sa non-linéarité vont permettre de restaurer le

signal, augmentant ainsi la marge de bruit et permettant

d’enchaîner des millions d’opérations sans

perte de l’information (c’est cette possibilité de

régénération qui donne ses avantages ŕ l’électroni-

que digitale par rapport ŕ l’analogique). Le fait que

le transistor ait trois électrodes permet de restaurer

ŕ chaque étape le signal en référence au niveau de

la tension d’alimentation.

Le courant de fuite - Un transistor utilisé

pour le traitement de l’information logique fonctionne

pour l’essentiel comme un interrupteur commandé

électriquement. On peut en effet montrer

(algčbre de Boole) que l’on peut réaliser toute opération

logique avec un ensemble d’interrupteurs.

Ce fonctionnement du transistor est obtenu en

commandant le passage de courant entre deux

régions de matériau semiconducteur séparées par

une barričre de potentiel. Le transfert de charges

est contrôlé par la modulation de la hauteur de la

barričre au moyen d’une tension appliquée. Si l’on

veut que les états "passant" et "bloquant" du transistor

soient nettement différents, cette barričre

d’énergie doit éviter que les charges ne transitent

involontairement quand le composant ne conduit

pas (courant de fuite émetteur - collecteur dans les

transistors bipolaires, courant de fuite source –

drain dans les MOS). Une autre source de courant

de fuite provient du courant existant entre l’électrode de commande du transistor et sa sortie (courant

de base du transistor bipolaire, courant de grille du

MOS). Malheureusement, en réduisant les dimensions,

ces courants de fuite augmentent et, en l’absence de sophistication dans la conception des

transistors, peuvent devenir du męme ordre de

grandeur que le courant actif. Les nouveaux

concepts de composants n’échappent pas ŕ ces

contraintes et le rapport des courants entre états

passant et bloqué d’un composant basé sur un

transfert de charges est un critčre essentiel de tout

composant appelé ŕ ętre utilisé dans un systčme

numérique.

La puissance consommée - Comme on le

verra par la suite, la puissance consommée est le

facteur limitant la performance des circuits intégrés,

pour une génération donnée. Un des avantages

essentiels du systčme de transistors MOS

complémentaires (le CMOS), qui a rendu cette

technologie dominante depuis une vingtaine d’années, est la possibilité de fonctionner sans courant

débité au "repos", quand on ne fait pas d’opération

logique (dans la paire de transistors complémentaires,

quand l’un est conducteur, l’autre est bloqué,

et aucun courant ne passe dans les transistors

(sauf les courants de fuite)). La seule consommation

apparaît lors de la commutation de l’état des

transistors, lorsque le transistor conducteur devient

bloqué et vice-versa. L’énergie consommée par

paire de transistors est alors approximativement

1/2 CV2dd ŕ chaque commutation, C étant la capacité

des deux transistors et Vdd la tension d’alimentation. La puissance dynamique est proportionnelle

au produit de la fréquence de fonctionnement

(imposée par des considérations systčme) par la

capacité totale ŕ charger et par le carré de Vdd.On

comprend ainsi l’intéręt de réduire la tension d’alimentation. Il faut cependant ce faisant garder une

marge de bruit suffisante (cela nécessite un seuil

de passage ŕ l’état conducteur bien défini, avec

non-linéarité de la tension de sortie par rapport ŕ la

tension d’entrée). Il existe par ailleurs une puissance

consommée statique (hors commutations logiques)

qui est proportionnelle au produit du courant

de fuite des transistors Ioff par la tension d’alimentation Vdd et

prend de plus en plus d’importance au

fur et ŕ mesure de la miniaturisation

Le temps de réponse d’un circuit est moins déterminé

par le temps de commutation intrinsčque d’un

élément, la porte logique (souvent caractérisé par

le paramčtre CV/I intrinsčque du composant) que

par le temps que la porte élémentaire va mettre

pour charger les interconnexions avec les autres

éléments (caractérisé par le produit RC de la résistance

et de la capacité de la ligne). Le gain du

transistor joue un rôle essentiel car il permet de

charger la grande capacité de la ligne plus rapidement

que ne le ferait le seul courant d’un composant

sans gain5.

Des compromis, toujours plus difficiles ŕ

réaliser, tendent ŕ rapprocher le transistor MOS réel

de ce bon transistor, composant idéal qui laisserait

passer un courant élevé en fonctionnement, qui

aurait un courant de fuite négligeable, un gain élevé

et une consommation faible, sans oublier un excellent

isolement entre l’entrée et la sortie. Si l’on ajoute

la nécessité d’un excellent contrôle des paramčtres

de fabrication pour que des millions de transistors

fonctionnent de maničre quasi identique, nous

trouvons cependant dans le CMOS classique beaucoup

des qualités que l’on demande au « bon »

composant.

Le gain apporté par la miniaturisation, et les

difficultés croissantes

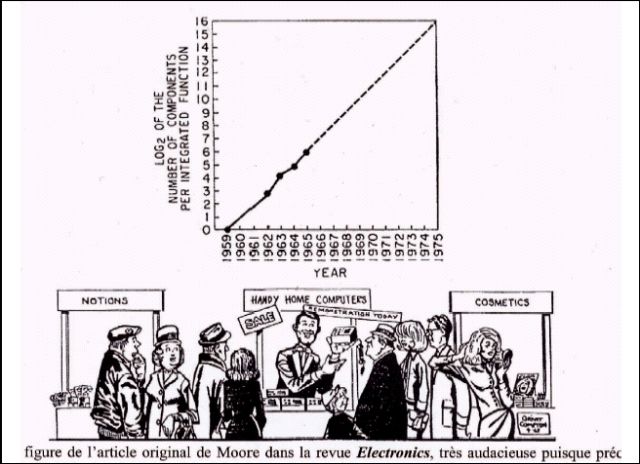

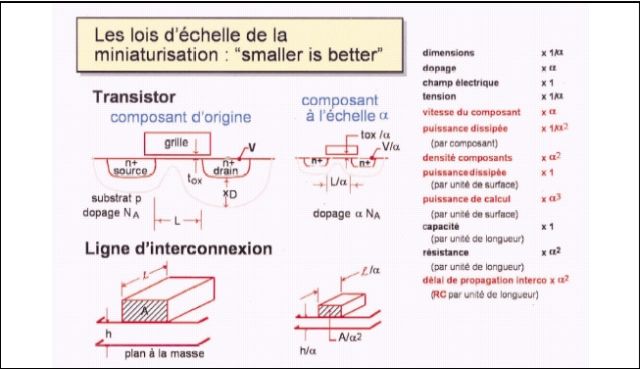

Abordé d’abord qualitativement, le gain

apporté par la miniaturisation, qui pouvait se résumer

par une intégration toujours croissante, a été

progressivement quantifié sous forme de lois

d’échelle. Concrčtement, quand les dimensions du

transistor sont divisées par un facteur α, la vitesse

est multipliée par un facteur α, la consommation

divisée par un facteur α, alors que la densité des

composants est multipliée par un facteur α2 6

(Figure 2). Du coup, la puissance de calcul augmente

comme α3, ŕ puissance consommée par

unité de surface constante ! Avec ces lois d’échelle

de la miniaturisation en microélectronique, "smaller

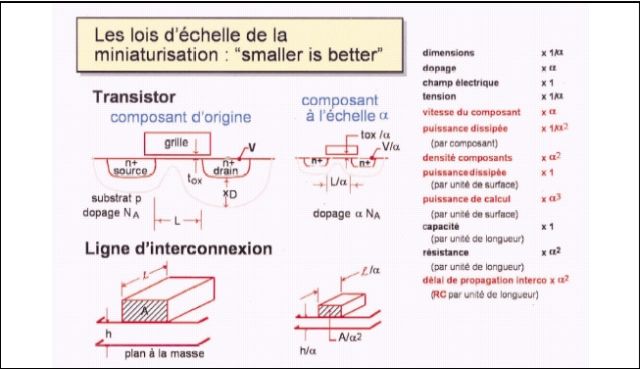

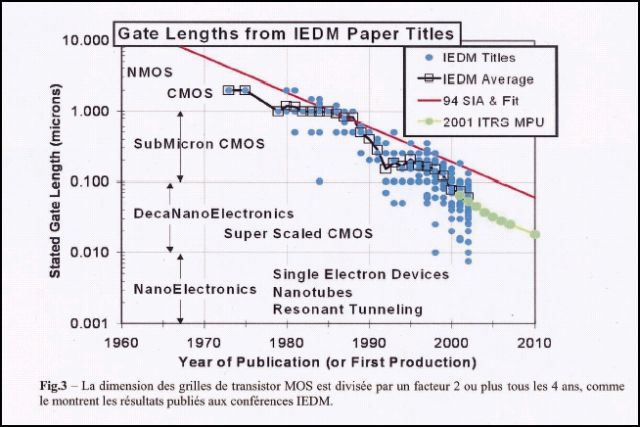

is better". Ce gain en performances lié ŕ la miniaturisation

pousse donc ŕ réduire les dimensions de

maničre trčs agressive (Figure 3). De fait, on observe

que pour les circuits rapides, de type microprocesseur,

la longueur de la grille du transistor a

diminué plus rapidement que la dimension caractéristique

du circuit (souvent associée au pas du

premier niveau d’interconnexion), elle-męme divisée

par deux tous les quatre ans7 .

Par contre, les męmes lois d’échelle mčnent

ŕ la conclusion que, pour une longueur constante, la

constante de temps des interconnexions est

multipliée par un facteur α. C’est bien ŕ longueur

d’interconnexion constante qu’il faut raisonner

quand on parle de vitesse de circuit puisque la surface

des puces est constante, et tend męme ŕ augmenter

pour les circuits haut de gamme, tels les

microprocesseurs, ce qui augmente la longueur

des grandes interconnexions. Pour parer ŕ cela, au

moins en partie, les circuits intégrés actuels utilisent

un systčme d’interconnexions "multi niveaux",

c’est ŕ dire une hiérarchie de sections suivant la

longueur de l’interconnexion, ce qui permet de

ne pas suivre les lois d’échelle pour les interconnexions

ŕ grande distance, dont les sections seront

plus grandes, et donc les résistances plus faibles.

D’autre part, le cuivre a remplacé l’aluminium pour

diminuer la résistance et des isolants de faible

constante diélectrique se sont substitués ŕ l’oxyde

de silicium pour minimiser les capacités et la diaphonie

entre lignes. Le domaine des connexions

sur la puce est un défi majeur de la microélectronique

que nous n’aborderons pas ici8.

On imagine sans peine que cette course

aux petites dimensions se décline en un grand

nombre de défis techniques qu’il faut relever. D’une

maničre assez unique, la communauté microélectronique

édite chaque année le consensus international

des buts technologiques ŕ atteindre pour

maintenir le rythme de gain en performances dans

la feuille de route de l’ITRS ; celle-ci a l’avantage

énorme de focaliser les ressources de la R&D

mondiale sur un nombre limité d’objectifs critiques,

tout en conservant la compétition entre acteurs. On

se reportera ŕ ce document pour une description

de ces défis9.

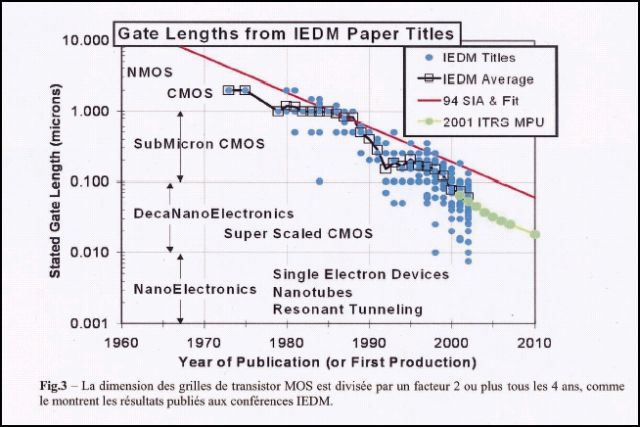

Quelques limites physiques des composants

classiques

Les transistors MOS les plus petits publiés

ŕ ce jour ont une longueur de grille de l’ordre de

5nm (remarquons que cela ne fait que 20 atomes

de silicium !). On peut légitimement se poser la

question : jusqu’oů ira-t-on dans cette miniaturisation

? Va-t-on se heurter ŕ des limites physiques infranchissables

?

Quand on analyse les architectures classiques de

MOS, réalisés actuellement sur du silicium massif,

on distingue plusieurs phénomčnes physiques

(Figure 4) qui contrarient le gain prédit par les lois

d’échelle, ou le "bon" fonctionnement du transistor.

La grille en silicium polycristallin ne se

comporte pas tout ŕ fait comme une électrode

métallique : une zone de déplétion augmente

l’épaisseur électrique effective de l’oxyde de grille,

rendant le couplage électrostatique entre la grille et

le canal moins effectif. Amincir l’oxyde de grille peut

diminuer cet effet dans une certaine limite, mais

au-dessous d’une certaine épaisseur, de l’ordre du

nanomčtre, le courant tunnel ŕ travers l’isolant

devient trčs prohibitif.

Plusieurs phénomčnes sont liés ŕ l’existence de champs électriques locaux inhomogčnes

de plus en plus forts10, détériorant la mobilité des

porteurs et induisant différentes formes de courant

de fuite (comme le courant tunnel bande ŕ bande)

et une dégradation de la fiabilité par l’injection de

porteurs chauds dans l’oxyde sous forme de

défauts chargés stables.

Un fort dopage du canal devient essentiel

pour éviter une action trop forte du potentiel du

drain dans le canal (dit effet canal court), réduisant

encore la mobilité des porteurs. De męme, les

source et drain doivent ętre fortement dopés pour

réduire la résistance d’accčs, et il serait souhaitable

aujourd’hui d’obtenir des concentrations supérieures

ŕ la solubilité limite de ces męmes dopants.

De la męme maničre la grille ne peut plus ętre

assez dopée pour lui assurer une résistance faible.

Tous ces problčmes font dire qu’il est peu probable

que le transistor sur silicium massif puisse fournir

le gain en performance attendu par une miniaturisation

pour les nœuds au dessous de 65nm.

Des solutions existent pour la plupart de ces problčmes

(par exemple la réduction de la tension

d’alimentation associée ŕ un substrat silicium sur

isolant ou SOI), nécessitant cependant des technologies

de plus en plus complexes et précises. C’est

ainsi que l’on explore des structures nouvelles de

transistors comme le transistor SOI ultra mince

(ultra thin body SOI, UT-SOI), le transistor SOI ŕ

double grille, voire ŕ triple grille (le FIN-FET par

exemple). L’obstacle aujourd’hui non résolu reste le

courant de fuite dans la grille : le remplacement de

ce systčme physique quasi-parfait qu’est l’interface

Si/SiO2 par un diélectrique de plus forte permittivité

comme le HfO2 (Figure 5) entraîne un certain

nombre d’effets secondaires (comme la réduction

importante de mobilité des porteurs), qui rendent

cette transition délicate dans un futur proche. On

ne change pas impunément un matériau qui a fait

le succčs du silicium face au germanium et aux III-

V et qui a été optimisé pendant des décennies.

Des phénomčnes physiques plus fondamentaux

prennent une importance accrue : avec la

diminution de taille, on voit apparaître des effets

statistiques ou quantiques : la faible dimension

entraîne des fluctuations statistiques relatives plus

importantes, comme par exemple les variations de

potentiel associées au faible nombre de dopants

dans un canal11 (3 atomes seulement dans un

canal de transistor UT-SOI de 6 nm par 10 nm ,

avec une épaisseur de silicium de 5nm, pour un

dopage de 1019 cm-3). L’augmentation du champ

électrique entre grille et canal entraîne une plus

forte localisation des porteurs ŕ l’interface silicium

/isolant. Cela mčne ŕ une quantification des

niveaux des électrons dans le canal, phénomčne

dont on sait tenir compte dans les outils de simulation,

mais surtout une nette dégradation de la

mobilité des porteurs, et donc de la résistance et

de la transconductance, ŕ cause de l’influence

accrue du désordre d’interface. On cherche ŕ y

parer en utilisant des canaux en hétérostructures

SiGe, ou bien du silicium contraint. Dans les deux

cas, on utilise du matériau ŕ plus grande mobilité

de départ, avant structuration. Cela se fait bien sűr

au prix d’une complexité de fabrication accrue.

La miniaturisation de l’autre composant

essentiel en microélectronique, le condensateur de

l’élément de mémoire dynamique DRAM, pose

aussi problčme : pour garder une information « lisible

» dans une cellule mémoire, avec une marge

au bruit suffisante, il faut de l’ordre de 300 000

électrons, ŕ préserver męme quand la surface de la

cellule et la tension d’alimentation diminuent avec

les lois d'échelle. Cette contrainte provient des exigences

de la méthode de mesure du bit de mémoire : on mesure la charge stockée par le condensateur

par un élément détectant cette charge situé en

bout d’une ligne de connexion qui ne change pas

de taille, ou męme augmente, avec la miniaturisation.

Cela pousse ŕ imaginer des structures trčs

sophistiquées pour garder cette quantité de charge

dans une surface occupée de la puce en diminution

constante, en étendant la capacité de stockage

dans la troisičme dimension et en utilisant des diélectriques

de trčs forte permittivité comme les

perovskites et des électrodes métalliques.

D’une maničre générale, la réponse apportée

aux problčmes d’optimisation du transistor aux

petites dimensions va dans le sens d’une complexification

des structures ŕ réaliser, ainsi qu’une diversification

importante des matériaux ŕ introduire.

Alors que la microélectronique s’est contentée du

silicium, de son oxyde et de l’aluminium comme

matériau de base pendant des décennies, on

observe aujourd’hui ce que certains appellent un

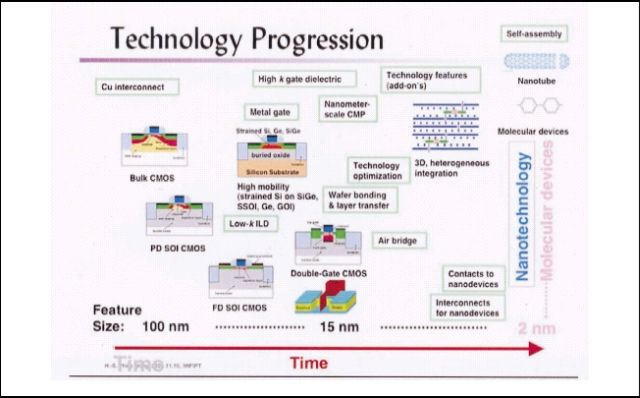

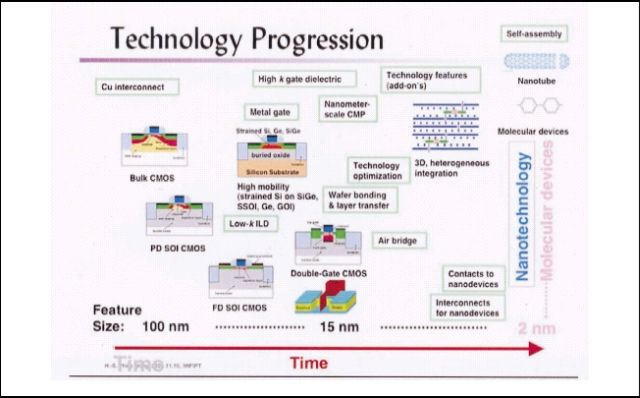

big bang des options ŕ développer (Figure 6).

On voit donc que « petit » va encore longtemps

signifier « meilleure performance », mais au prix

d’un effort de R&D largement accru et la mise en

place de solutions technologiques de plus en plus

compliquées et coűteuses.

Certains problčmes ne trouvent cependant

pas une réponse satisfaisante qui soit purement

technologique, c.a.d. hardware. La puissance

consommée en est un bon exemple. Si l’on extrapole

la puissance consommée par des circuits rapides

comme les microprocesseurs, on conclut vite

que la densité de puissance va croître dans des

proportions totalement déraisonnables (Figure 7).

Des solutions existent comme de diminuer

localement la tension de seuil, par exemple en

polarisant le substrat (une réduction de la puissance

consommée de 2 ŕ 10 est possible), ou de couper

l’alimentation des transistors inactifs (gain

attendu de 2 ŕ 1000). Toutefois chaque approche a

ses propres contraintes en terme de complexité

technologique, de vitesse notamment liée ŕ la

réactivation des transistors en mode actif.

Il faut enfin signaler le conflit entre puissance

consommée par opération et flexibilité d’utilisation :

les circuits dédiés sont en effet beaucoup moins

gourmands en énergie que les circuits programmables

(Figure 8). Cela montre d’une part l’impact des

architectures, d’autre part la difficulté sous-jacente

ŕ faire fonctionner une machine universelle de traitement

de l’information avec, pour chaque tâche,

l’efficacité d’une machine spécialisée. On peut

cependant considérer tout cela comme des bonnes

nouvelles : en mettant bout ŕ bout les éléments que

l’on vient d’énoncer (contrôle des tensions de seuil,

alimentation des seuls éléments actifs ŕ un

moment donné, architectures optimisées), il y a un

gisement d’amélioration de l’ordre du million, hors

gain dű ŕ la miniaturisation.

Au delŕ de la microélectronique "classique" de

la feuille de route : les composants émergents

Les composants émergents de la feuille de

route ITRS

Ce n’est pas d’aujourd’hui que les chercheurs

ont imaginé des composants innovants,

souvent présentés comme une alternative au

MOS12. Alors que le transistor MOS va continuer ŕ

évoluer jusqu’ŕ des dimensions de l’ordre de 10nm

ou moins, la question se pose de savoir si des composants

radicalement différents prévaudront ŕ des

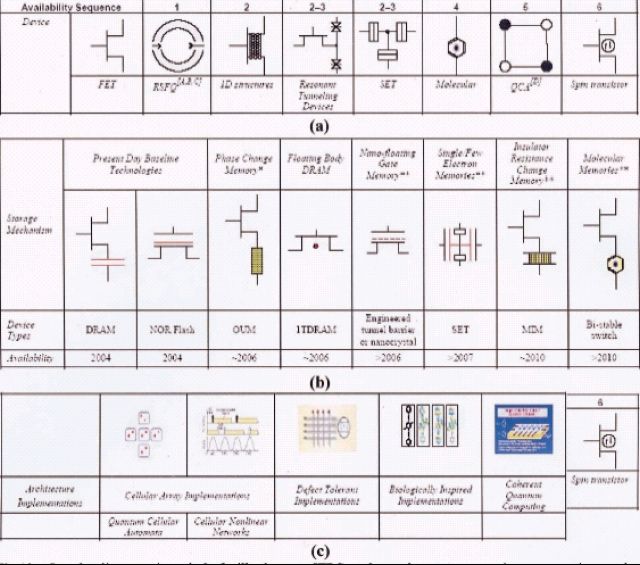

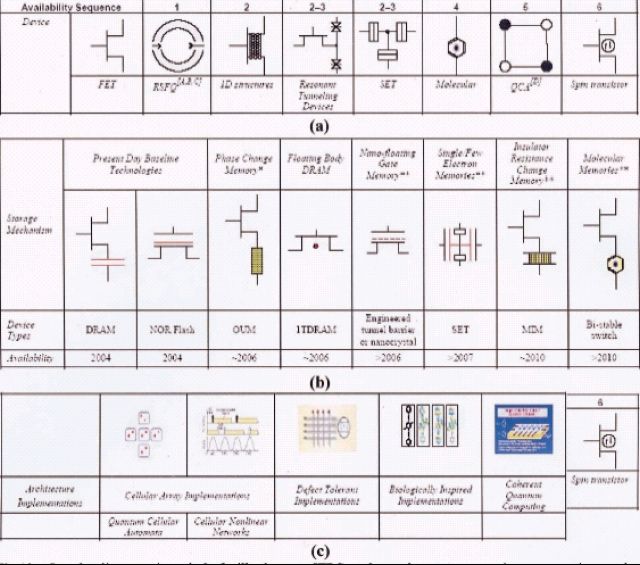

dimensions inférieures (Figure 9).

La feuille de route, dans ses derničres versions,

a commencé ŕ recenser les options disponibles

en termes de dispositifs logiques (Figure 10a),

de mémoires (Figure 10b) et d’architectures associées

(Figure 10c). La sélection s’est faite sur la

base du nombre de publications, qui est censé traduire

l’intensité de la recherche sur ce type de

composants. Une synthčse critique a été ensuite

réalisée en analysant les potentiels et les risques

de chaque approche au regard des performances,

de la puissance consommée, de la sensibilité aux

paramčtres de fabrication et de fonctionnement,

des perspectives de miniaturisation, ainsi qu’ŕ la

capacité ŕ s’intégrer au CMOS et aux architectures

actuelles.

La conclusion tirée des informations

actuellement disponibles est qu’aucun composant

"alternatif" ne devrait concurrencer le CMOS dans

les grands circuits de traitement logique, tels les

microprocesseurs, ŕ moins que l’on ne parvienne ŕ

mettre en oœuvre des composants moléculaires

dans de nouvelles architectures13 , ce qui augmente

largement l’incertitude de ces technologies.

Dans des architectures traditionnelles, les éléments

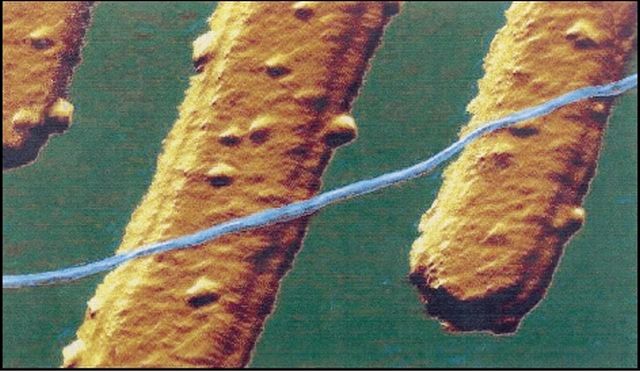

les plus prometteurs pourraient ętre des

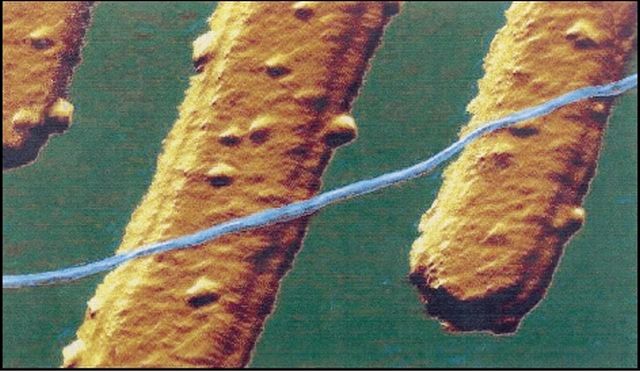

systčmes unidimensionnels de type nanotubes de

carbone (Figure 11) ou nano-fils semiconducteurs

qui fonctionnent comme des MOS, avec comme

avantages des modes de fabrication et des architectures

trčs différents (cf. le rapport d’aspect diamčtre/longueur).

Le constat est moins pessimiste pour les

mémoires, que l'on doit cependant séparer en deux

familles trčs différentes : d’un côté, les nouveaux

éléments proposés oů la mémorisation repose sur

un principe nouveau14 : mémoires ferromagnétiques,

ferroélectriques, ŕ changement de phase,

mais dont l’architecture reste similaire aux mémoires

actuelles. On a remplacé le condensateur

dynamique des DRAM (qui pourrait arriver en

butée pour le nœud de 50 nm14) par un domaine

ferroélectrique ou ferromagnétique, ou bien un

domaine cristallin ou amorphe. L’avantage par rapport

aux DRAM est le caractčre permanent de la

mise en mémoire, les problčmes ŕ résoudre4 sont

ceux de la fabrication en masse, de la fiabilité, des

lois d’échelle du fonctionnement, etc. Les autres

concepts apparaissent beaucoup plus lointains,

comme les mémoires moléculaires et celles qui

font appel ŕ un/ quelques électrons, et qui nécessitent

sans doute de nouveaux systčmes de lecture

et des nouvelles architectures.

D’autres porteurs d’information que la

charge de l’électron ont été envisagés comme le

spin, le photon, la phase d’un état quantique, etc.

mais ces approches sont trop embryonnaires (bien

que parfois anciennes comme l’ordinateur optique)

pour qu’il soit aujourd’hui possible de conclure si

elles répondent aux critčres du « bon » composant

dans des architectures classiques de traitement de

l’information, ou utilisables dans le monde réel

avec d’autres architectures.

On peut au fond résumer les questions ŕ

résoudre pour valider un nouveau concept de technologie

supposée remplacer une technologie existante,

comme le CMOS de la microélectronique,

dans les termes de Goronkin16 , un apôtre (pourtant)

de l’électronique moléculaire :

1- Les résultats doivent ętre reproduits facilement

en laboratoire

2- Il existe une compréhension de base du fonctionnement

du composant et des procédés de

fabrication

3- Les nouveaux composants doivent avoir une

performance supérieure ŕ ceux existant, dans leur

forme présente et dans leurs évolutions prévisibles.

4- On peut entrevoir un cheminement par lequel

cette technologie réalisera une percée sur le marché

et sera compétitive en termes de coűt.

En conclusion un transistor MOS « idéal »

ŕ grille enveloppante ("surrounding gate"), comme

dans la (Figure 12), semble rester encore le meilleur

candidat « ultime » pour le traitement d’informations.

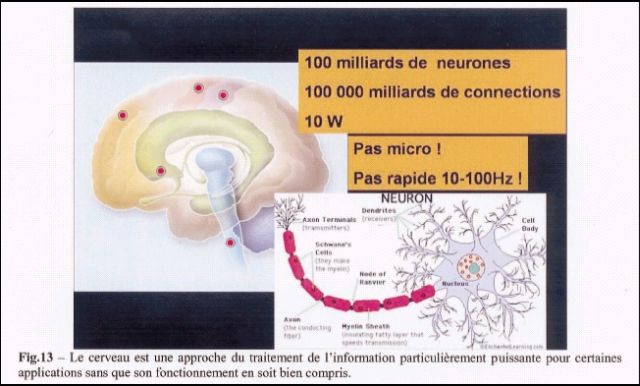

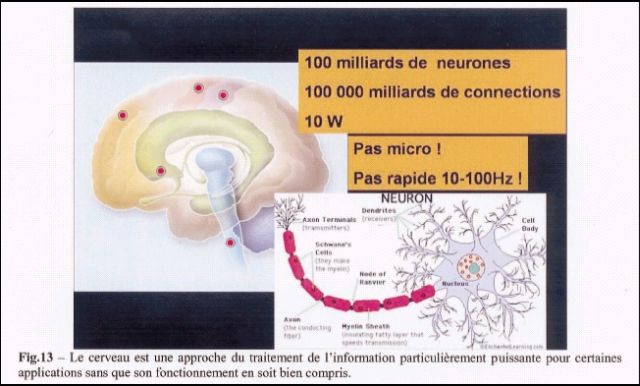

Quelques mots sur une approche tout ŕ fait

différente de traitement de l’information et de

mémorisation, le cerveau (Figure13), qui reste

pour une bonne part une machine de traitement de

l’information encore trčs largement incomprise.

Tout d’abord, ce n’est pas une machine d’électronique moléculaire au sens oů on l’entend

aujourd’hui, c’est ŕ dire avec des molécules uniques

ayant des propriétés de traitement de l’information : le neurone, avec des milliers de synapses

et des longueurs allant jusqu’au mčtre, n’est certainement

pas nanométrique. Il n’est pas non plus

rapide puisque la fréquence des signaux est de

l’ordre de la centaine de Hz. Enfin, chaque opération

élémentaire consomme une énergie trčs largement

supérieure ŕ celle d’un transistor moderne : la

commutation d’une synapse nécessite 17 de dégrader

de l’ordre de 100 000 molécules d’ATP, chacune

fournissant 22 kT, soit 15 fJ.

L’efficacité du cerveau repose donc sur

bien autre chose que la miniaturisation ou la performance

de ses composants élémentaires. Il faut tout

d’abord insister sur le fait que la transition d’une

synapse réalise une opération complexe : elle est

analogique, et représente plusieurs bits élémentaires

en logique binaire (le défaut associé est que le

signal se dégrade lors de la propagation, alors

qu’un signal digital, étant restauré, peut se propager

ŕ l’infini dans un circuit intégré). Elle correspond

ŕ un nombre de stimuli d’entrée qui peut ętre

trčs élevé, et représenter ainsi le fruit d’une algorithmique

complexe. Cette multiplicité, certainement

comprenant de la redondance, permet la

correction d’erreurs et la fiabilité ŕ long terme (hors

perte massive de neurones fonctionnels comme

dans les maladies de Parkinson et d’Alzheimer).

L’architecture du cerveau est trčs efficace et structurée

: on sait grâce ŕ l’imagerie fonctionnelle que

les aires du cerveau sont spécialisées.

L’architecture est tridimensionnelle et évolutive (la

croissance et l’interconnexion ont lieu jusqu’ŕ 2 ans

pour l’essentiel). La puissance de calcul provient

en partie d’interconnexions trčs performantes : le

débit maximum pourrait atteindre 1Tb/s (jamais

atteint en pratique ŕ cause du coűt énergétique).

La connectique est sélective, ce qui permet d’avoir

une architecture plus riche pour des nombres de

neurones et synapses donnés. Seule une partie

des neurones fonctionne ŕ un instant donné (de 1

ŕ 16 %), ce qui permet de limiter la puissance

nécessaire ŕ 15-20 W. On voit que beaucoup d’éléments, trčs différents de nos machines artificielles,

donnent son efficacité au cerveau, dont on ne

connaît qu’une toute partie du puzzle, et que bien

les solutions trouvées par le cerveau aux défis du

traitement de l’information et de mémorisation

pourraient ętre utiles dans nos machines.

Une question reste posée. Dans une vingtaine

d’années, si le progrčs de la microélectronique

se poursuit, on pourra peut-ętre acheter pour

mille euros l’équivalent, en puissance de traitement,

d’un cerveau humain. Pourra t’on aller plus

loin ? la puissance de calcul du cerveau, venant

d’une longue optimisation lors de l’évolution, n’est

elle pas le résultat de ce que permettent les lois

physique pour une puissance dissipée de 15-20 W,

pour un certain type de « fabrication », et pour un

taux d’erreurs donné, aprčs correction. Dans ce

cas, le CMOS (et toute autre solution) ne pourrait

atteindre cette performance que par des composants

et architecture complčtement différents du

cerveau. Tout au plus aurait-on peut ętre une amélioration

(d’un ordre de grandeur ?) du fait des

contraintes de fabrication trčs différentes.Il ne semble

pas qu’il existe aujourd’hui une réponse ŕ cette

question.

Existe-t-il des limites physiques intangibles ?

De nombreux articles essaient de répondre ŕ cette

question de maničre plus ou moins détaillée (ou

convaincante, selon les goűts). On peut les résumer

de la maničre suivante pour un composant fonctionnant

ŕ température ambiante 18, 19 :

- l’énergie de commutation Ebit ne pourrait pas ętre

inférieure ŕ k.T.ln2, soit 3.10-21 J ou 17 meV ŕ

température ambiante (énergie de commutation

minimum pour un ordinateur irréversible20). Le

besoin de discernabilité de l’état du composant ŕ

température ambiante nécessiterait plutôt une énergie

de l’ordre de 0.5 eV.

-la taille minimale Δx ne devrait pas ętre inférieure ŕ

1,5nm21 . Ceci est déduit de l’incertitude en

position (premičre relation d’incertitude d’Heisenberg

Δx.Δp ≥h) découlant de l’énergie minimum de commutation et de l’incertitude Δp associée.

- le temps de transit intrinsčque minimum tmin

serait de 40 fs (en utilisant la deuxičme relation

d’incertitude d’Heisenberg ΔE.Δt ≥ h )

- la densité de composant nmax, déterminée par

1/ (Δx)2 (approximation trčs grossičre) est alors de

5. 1013 composants par cm2,

ce qui induirait une consommation

E= nmax.Ebit/tmin de 4.7 MW/cm2, si toutes ces limites

étaient atteintes simultanément.

Il est clair qu’une telle discussion des limites,

bien qu’intéressante, car montrant des limites

indépendantes du matériau et des dispositifs utilisés,

est par trop simpliste. Une analyse plus approfondie19

prend plutôt comme paramčtres de départ

la puissance dissipée, les matériaux utilisés, la longueur

des interconnections et la vitesse de la

lumičre, etc. De plus, comme nous l’avons discuté

plus haut, il n’y a pas de raison de considérer que

la maničre ultime de satisfaire aux contraintes suppose

d’utiliser un ensemble uniforme de composants

et de tensions de commande, bien au

contraire. C’est pourquoi la discussion des limites

physiques fondamentales, si elle donne des informations

incontournables sur le « possible », ne

permet pas de s’affranchir de l’étude des possibilités

ultimes en faisant une analyse détaillée, dispositif

par dispositif, matériau par matériau, algorithme

par algorithme, architecture par architecture.

Pour quelles applications ?

On peut se demander si cette course ŕ la

miniaturisation aura toujours une raison d’ętre, vu

les difficultés de plus en plus fondamentales auxquelles

on se heurte. Il faut aussi se demander s’il

existera des besoins solvables pour se payer des

technologies de rupture par rapport au silicium ultime,

qui nécessiteront de nouveaux investissements

au moins équivalents ŕ ceux qui sont faits

depuis l’origine de la microélectronique, pour mettre

en œuvre ces technologies, car il n’y a que peu

de raisons de penser que leur mise en œuvre sera

moins onéreuse, sans compter les risques associés.

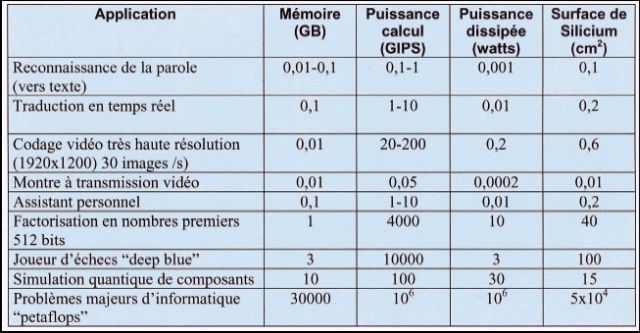

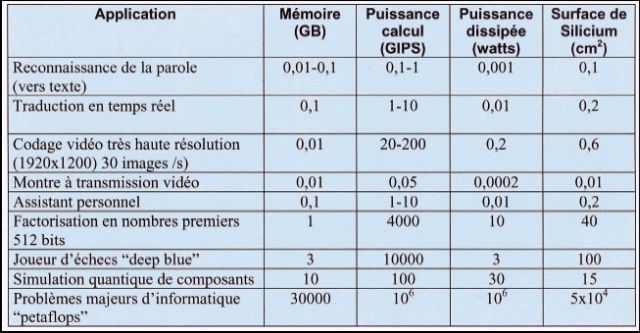

La réponse est mitigée, si on en croit la Figure

14 : seules des applications trčs spéciales

devraient exiger des puissances de calcul au delŕ

de ce qui sera accessible pour des surfaces de

puces standard, de l’ordre du cm2.

La connexion avec le monde extérieur

Quelque soit la puissance de calcul, les unités

de traitement doivent ętre interfacées avec le

monde extérieur. Cela nécessite souvent des circuits

d’interface complexes et mélangeant les technologies

: puissance, RF, opto, etc. Les technologies

matérielles (le "hardware") des interfaces homme –

machine (IHM) sont aussi trčs intéressantes du point de

vue scientifique et technologique, et représentent

d’énormes marchés. C’est lŕ oů l’Europe et notamment

la France ont contribué significativement au

niveau de la recherche au moins, et pourraient peut-ętre

continuer ŕ le faire, voire ŕ ętre plus présents

sur le terrain industriel, dans le partage des tâches

au niveau mondial qui semble s’esquisser.

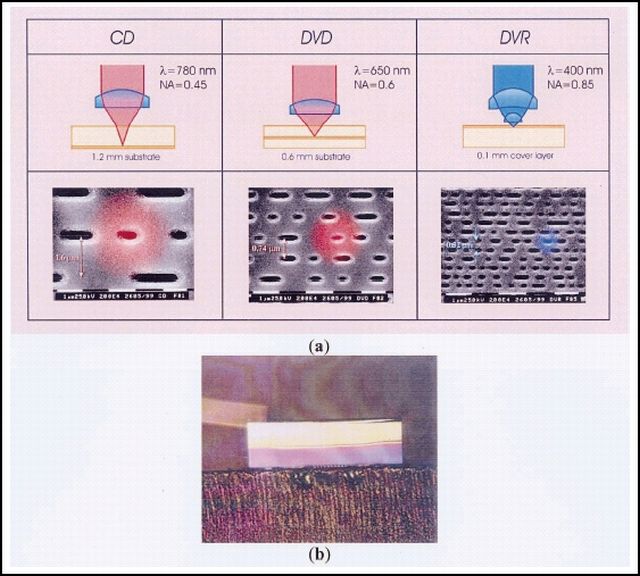

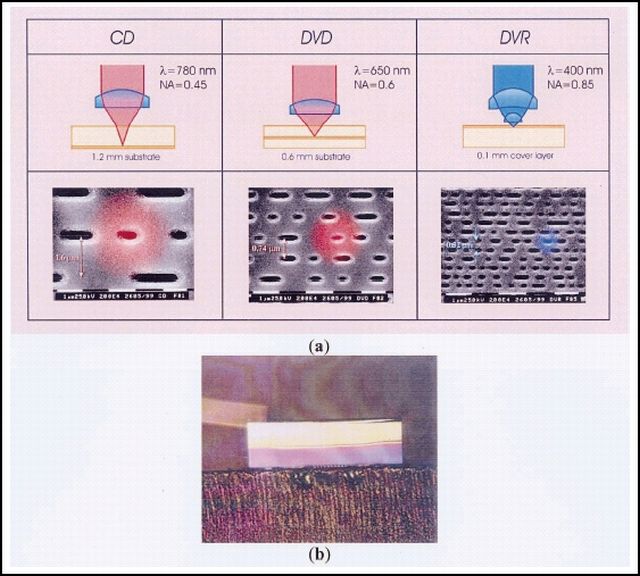

Comme exemple de recherches passées

ou présentes, mentionnons, dans le domaine de

l’enregistrement optique (Figure 15), et męme au

delŕ du concept d’enregistrement optique des

années 70, la premičre industrialisation du laser ŕ

puits quantiques chez Thomson-CSF en 1986. Ce

laser est aujourd’hui omniprésent, du lecteur de CD-

ROM aux télécommunications optiques. Dans ce

dernier domaine, des équipes de premier plan travaillent

sur l’optique intégrée, devant permettre l’in-

tégration ŕ grande échelle, comme par exemple

avec les cristaux photoniques (Figure 16). Le défi est

aujourd'hui de manipuler les données provenant des

fibres optiques de maničre totalement optique, car

les conversions optique – électrique – optique sont ŕ

la fois trčs complexes et onéreuses, pour des capacités

de transmission aujourd’hui de 10 Tb/s par

fibre, multiplexées sur des centaines de longueurs

d’ondes différentes. Pour y parvenir, il faut pouvoir

fabriquer des circuits intégrés optiques actifs et passifs

ŕ grande fonctionnalité. Or le confinement optique

dans les structures diélectriques habituelles est

« faible » (le confinement diélectrique ne permet pas

de guider efficacement la lumičre, par exemple dans

des virages trčs serrés, de rayon de courbure de l'ordre de la longueur d'onde). Du coup, les circuits intégrés

optiques sont trčs grands (jusqu’ŕ quelques

dizaines de cm2) pour un nombre limité de fonctions

(jusqu’ŕ une centaine). Pour atteindre ŕ des densités

nettement plus élevées, l’approche des cristaux photoniques22

se propose de contrôler la propagation

de la lumičre dans des milieux dont la constante diélectrique

est périodique, ŕ la maničre dont les cristaux

habituels contrôlent la propagation des électrons

dans des bandes d'énergie permise et interdite.

De la męme maničre, en enregistrement

magnétique24, la magnétorésistance géante (Figure 17), qui est ŕ la base des tętes de lecture

de disques durs modernes, a été découverte en

France. Les laboratoires de Zürich d’IBM travaillent

ŕ l’écriture sur un médium avec une résolution

nanométrique en utilisant une matrice de nanopointes

pour écrire et lire l’information par nano

indentation de matériaux thermoplastiques, dérivée

du microscope ŕ effet tunnel inventé chez eux25.

Bien d’autres exemples, permettant d’interfacer les

systčmes microélectroniques et le monde extérieur,

ont aussi un fort intéręt commercial.

Mentionnons le livre électronique sur substrat souple,

intégrant de l’encre électronique26 (collab. Eink

corp, MIT, Philips ; Figure 18) : il s’agit de réaliser

un afficheur passif (la luminance de l’affichage

est due ŕ la lumičre ambiante, comme pour le

papier) ayant l’ergonomie du livre avec ses feuilles,

grâce ŕ une modification locale des propriétés optiques

(absorption, diffusion, réflexion) commandée

par un champ électrique appliqué localement.

Aucun phénomčne électronique ou ionique ne réalise

des changements optiques suffisamment

intenses, et les principales réalisations sont basées

sur des déplacements de particules colorées par

des champs électriques (électrophorčse). La

consommation électrique est extręmement basse

car les particules restent en place grâce ŕ des

effets d’hystérésis. On ne consomme de l’énergie

que lorsque l’affichage est actualisé. Autre exemple

d’interface récent, la lentille électro-mouillante de

Philips27 qui permet d’obtenir une lentille variable

par application d’un champ électrique qui agit sur le

ménisque existant entre deux liquides (Figure 19).

On peut ainsi réaliser une lentille intégrée avec des

imageurs solides, permettant de faire des caméras

ŕ haute performance ŕ trčs bas coűt.

On peut imaginer beaucoup d’autres composants

de ce type, car ces interfaces se limitent

aujourd’hui essentiellement ŕ la vue et ŕ l’ouďe, les

autres sens et a fortiori des analyses de situations

plus complexes attendent les composants d’interface

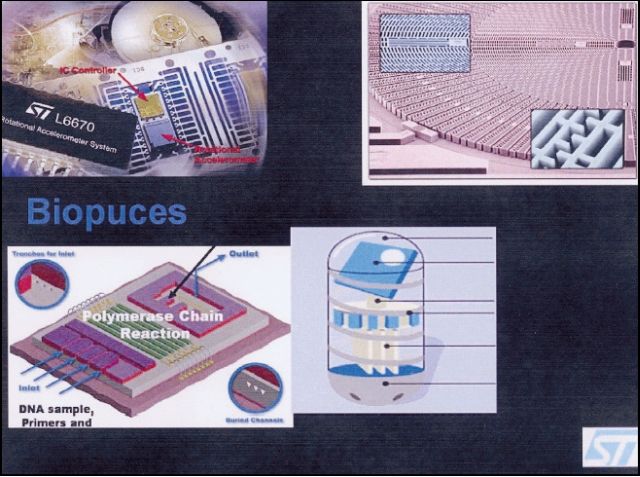

associés. Un exemple qui illustre cette problématique

peut ętre les biopuces qui feraient une analyse temps

réel de l’état du patient (sain ou malade !) et qui

retransmettraient les informations par une technique

sans fil au sein d’un ‘Body Area Network’ (Figure 20).

La détection et le suivi individuel des maladies

devraient permettre des gains spectaculaires sur la

qualité des systčmes de santé et sur leur coűt.

Enfin un autre domaine trčs important qui reste ŕ

développer est celui des sources d’énergie, notamment

pour les appareils nomades, incluant la récupération

d’énergie (par exemple ŕ partir de capteurs

piézoélectriques placés sous les chaussures28

), son stockage et son contrôle. Des programmes

trčs ambitieux sont lancés, comme le projet

Smart Dust29 de la DARPA qui cumule dans un

objet de l’ordre du cm3, tous les problčmes de capteurs,

de communication sans fils et d’énergie afin

d’obtenir des capteurs autonomes, communiquants

et distribués.

Conclusion

Il faut rester modeste dans notre perception du futur de

la microélectronique. Trop de prévisions se sont avérées

erronées en sous-estimant la capacité de l’homme ŕ surmonter les difficultés technologiques. Il a été

annoncé, suite ŕ une analyse sophistiquée tenant

compte par exemple des rayons cosmiques [Wallmark

1962] que les dimensions minimales des transistors ne

descendraient pas au-dessous de 10µm. Il a été prédit

par exemple que les mémoires en semiconducteurs

allaient supplanter les disques durs : c’était sans compter

sur les progrčs de l’enregistrement magnétique.

Des études ont montré que, vu les perpectives catastrophiques

de l’industrie européenne du semiconducteur

en l’an 2000, il fallait lancer en parallčle ŕ JESSI

des programmes sur l’électronique moléculaire, relancer

l’AsGa et se concerter sur l’ordinateur optique :

c’était sans compter le redressement spectaculaire de

l’industrie européenne qui a su hisser ses trois acteurs

industriels dans les dix premiers mondiaux.

Une chose semble cependant trčs probable : le MOS

sur substrat silicium a encore de beaux jours devant

lui. Comme décrit plus haut, il a un potentiel de miniaturisation

ŕ venir de 103, d’intégration (miniaturisation

+ taille de la puce) de 104, de capacité de calcul (ŕ

miniaturisation donnée) de 106 par l’optimisation

d’architecture, le contrôle des tensions d’alimentation

et tensions de seuil. A supposer que tous ces gains

soient réalisables simultanément, il a donc une

marge de progression de l’ordre de 109.

La révolution de la microélectronique est encore ŕ

venir !

Annexes

| Fig.1 – La figure de l’article original de Moore dans la revue Electronics, trčs audacieuse puisque prédisant une

augmentation de l’intégration de 64 composants par puce en 1965 ŕ 60 000 en 1975. Plus utopique encore, le

dessin humoristique accompagnant l’article, prédisant la vente au grand public d’ordinateurs portables !.

Rappelons qu’en 1977 encore, K. Olsen, le fondateur de Digital (l’entreprise ayant révolutionné le domaine des

ordinateurs par le mini-ordinateur), affirmait que personne n’aurait besoin d’un ordinateur personnel. Le dessinateur

était vraiment inspiré ! (©Electronics). retour |

Fig.2 – Les lois d’échelle de la microélectronique permettent de quantifier le gain attendu par la réduction des

dimensions. retour

Fig.3 – La dimension des grilles de transistor MOS est divisée par un facteur 2 ou plus tous les 4 ans, comme

le montrent les résultats publiés aux conférences IEDM. retour

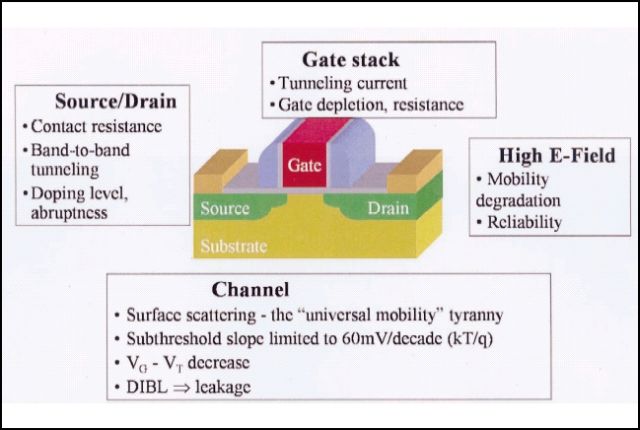

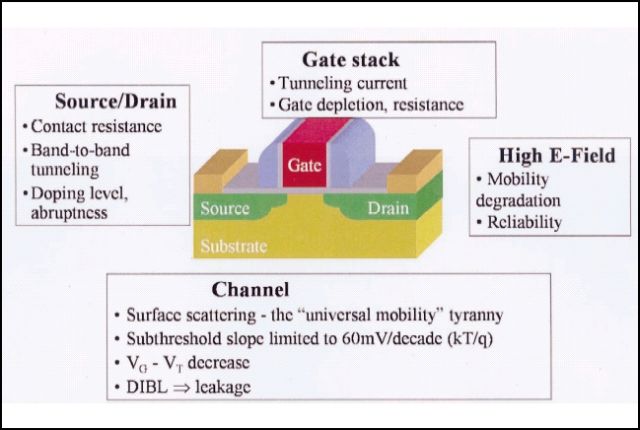

Fig.4 – Phénomčnes physiques limitant la performance des transistors MOS classiques aux petites dimensions. retour

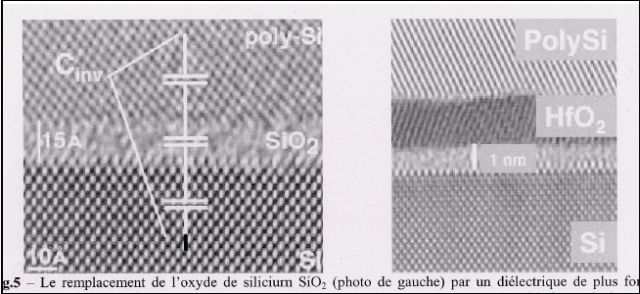

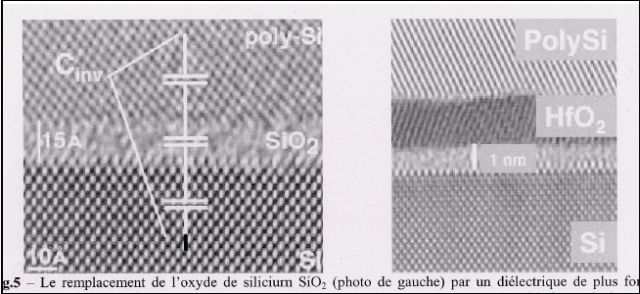

Fig.5 – Le remplacement de l’oxyde de silicium SiO2 (photo de gauche) par un diélectrique de plus forte permittivité

comme le HfO2 (photo de droite) se heurte ŕ des problčmes techniques aujourd’hui non résolus. retour

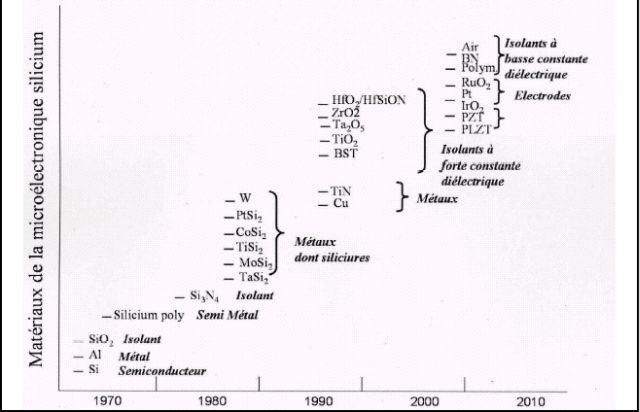

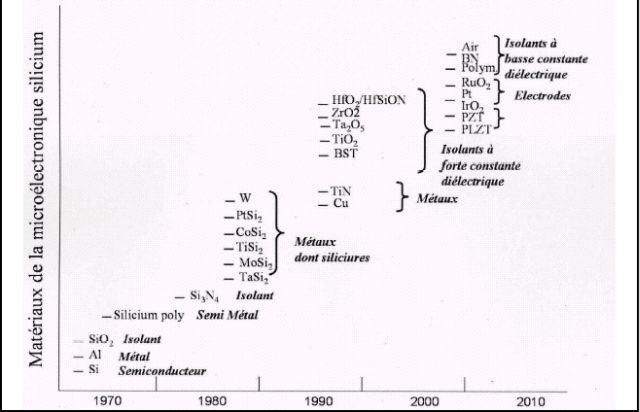

| Fig.6 – Le nombre de nouveaux matériaux ŕ introduire a augmenté de maničre importante ces derničres

années, pour réaliser des transistors performants de petites dimensions. retour |

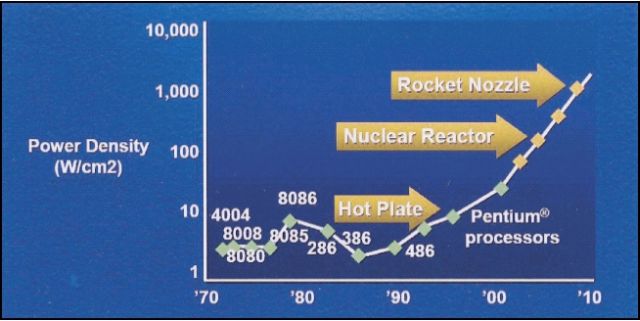

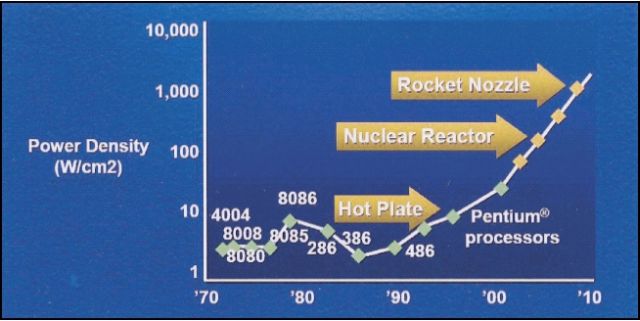

| Fig.7 – La puissance consommée par les circuits performants reste un problčme majeur qui ne peut ętre résolu

que par un travail conjoint des concepteurs et des technologues (ici une extrapolation des puissances des microprocesseurs

telle que présentée par Intel sur son site web pour souligner l’ampleur du problčme ŕ résoudre).retour |

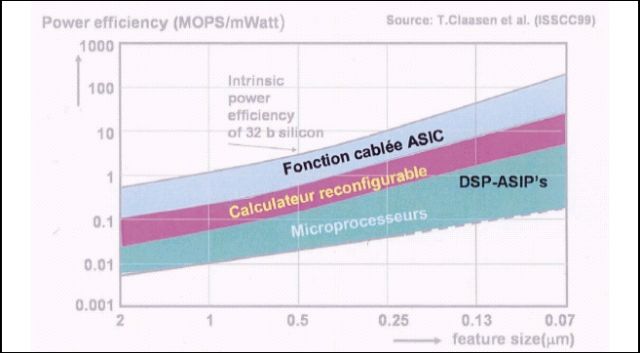

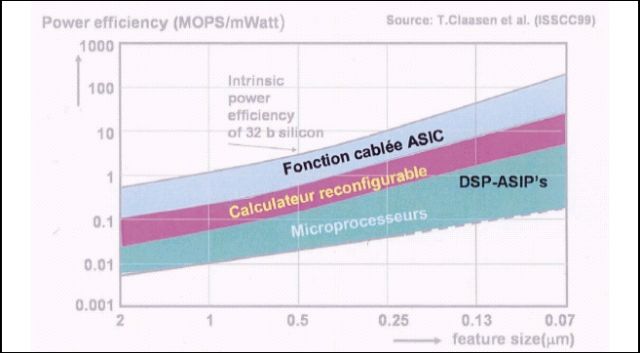

| Fig.8 – Les circuits dédiés dans lesquels les fonctions sont câblées montrent une bien meilleure efficacité énergétique

au détriment d’une flexibilité d’usage bien inférieure aux circuits programmables. retour |

| Fig 9 Au-delŕ de l’évolution de la structure du transistor MOS jusqu’ŕ une dizaine de nm, de nouveaux composants de

taille nanométrique doivent ętre explorés (d’aprčs Wong, IWFIPT 2003. retour |

| Fig.10 – Les derničres versions de la feuille de route ITRS analysent les composants émergents qui pourraient

apparaître ŕ l’échelle nanométrique.

(a) composants logiques retour

(b) mémoires retour

(c) architectures associées retour |

| Fig.11 – Les nanotubes de carbone (ici en bleu sur des électrodes en or

apparaissant en jaune) ont un potentiel intéressant pour des composants de

traitement de l’information (notamment un transport semble-t-il balistique), sous

réserve que l’on sache les positionner et faire croître de maničre contrôlée, avoir

des contacts de bonne qualité et reproductibles, et créer un réseau dense

d’interconnexions15 . Ils ont bien d’autres applications pour les affichages,

les cellules photovoltaďques, l’électrochimie, les matériaux composites, etc.

retour |

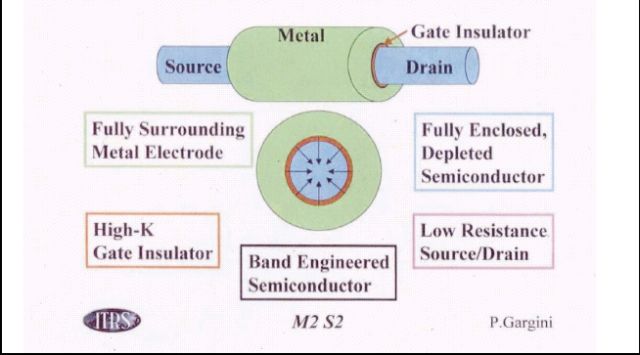

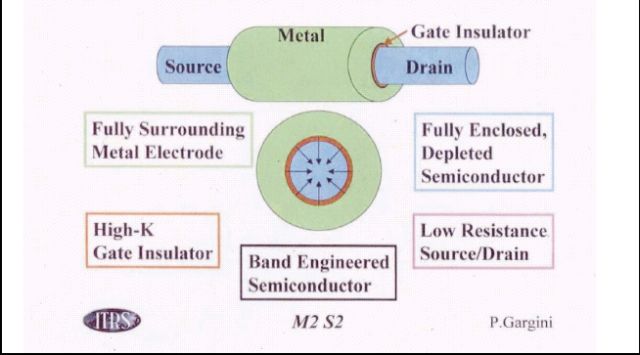

Fig.12 – Le transistor MOS idéal, ŕ grille enveloppante ("surrounding gate"), tel qu’imaginé dans la feuille de

route ITRS. retour

| Fig.13 – Le cerveau est une approche du traitement de l’information particuličrement puissante pour certaines applications

sans que son fonctionnement en soit bien compris. retour |

| Fig.14 – Seules certaines applications trčs spécialisées demandent des puissances de calcul qui sont au delŕ de ce

que permettra le silicium en 2016 suivant la feuille de route de 2001. La plupart des grandes applications seront satisfaites

avec des surfaces (donc des coűts) tout ŕ fait raisonnables (moyennant des progrčs simultanés en algorithmes). retour |

| Fig.15 – (a) : Certains composants nécessaires ŕ l’enregistrement optique ont été démontrés trčs tôt en

France comme le laser ŕ puits quantiques de Thomson-CSF commercialisé dčs 1986. (b) : Les progrčs

récents (a) du CD-ROM (650MB) vers le DVD (4.7 MB) et le blu-ray DVD (25 GB) proviennent de l’utilisation

de lasers ŕ plus courte longueur d’ondes, d’optiques corrigées ŕ plus grande ouverture, d’algorithmes

meilleurs de suivi des pistes23 . retour |

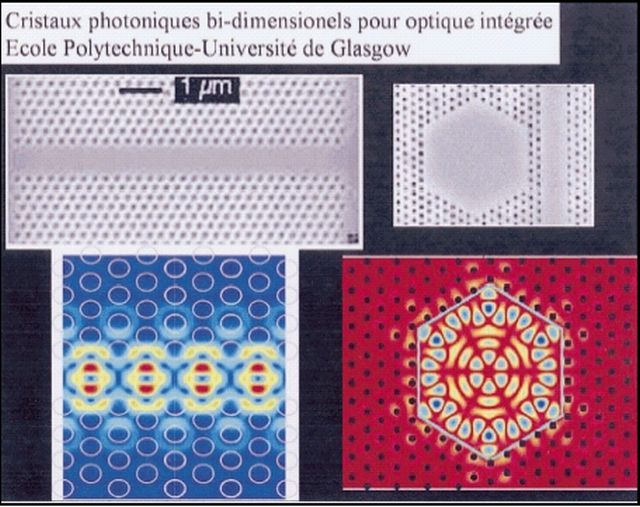

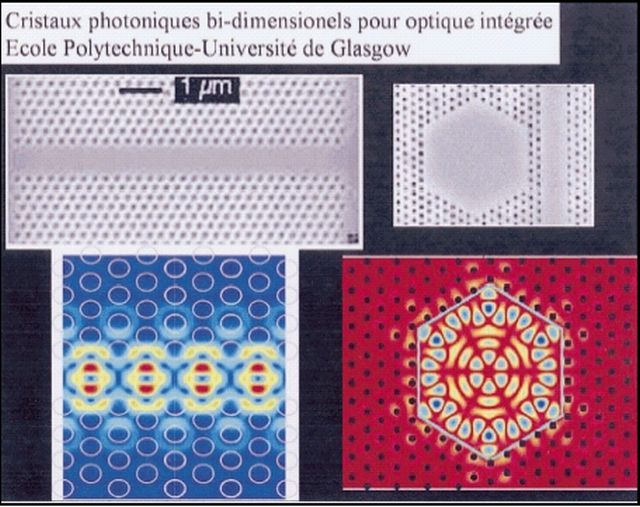

| Fig.16 – Les cristaux photoniques permettent de confiner efficacement la lumičre

et ainsi la guider. On voit, en haut ŕ gauche un guide d’ondes planaire, en haut ŕ

droite une microcavité hexagonale planaire, tous deux réalisés par des cristaux

photoniques triangulaires air/semiconducteur, dans des hétérostructures

GaAs/GaAlAs, et en dessous la simulation de leurs champs électriques. retour |

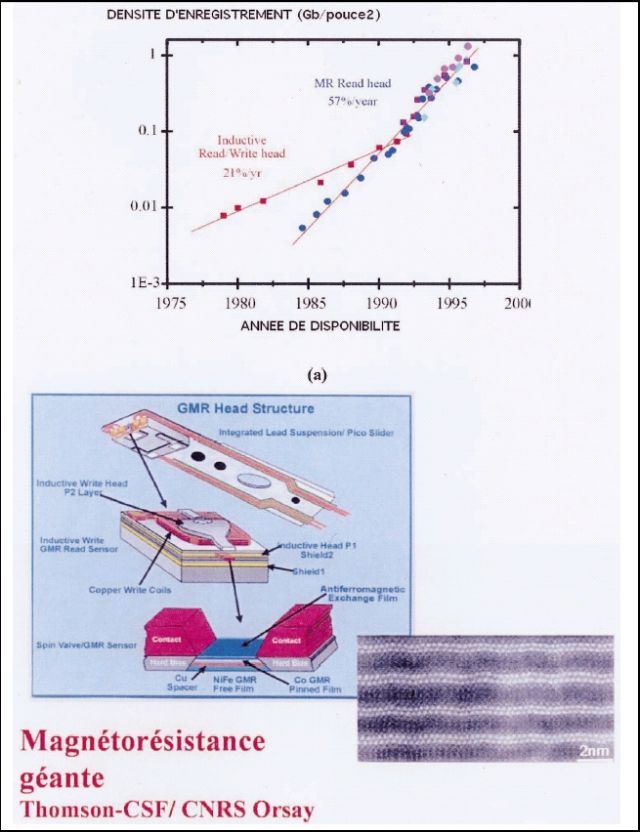

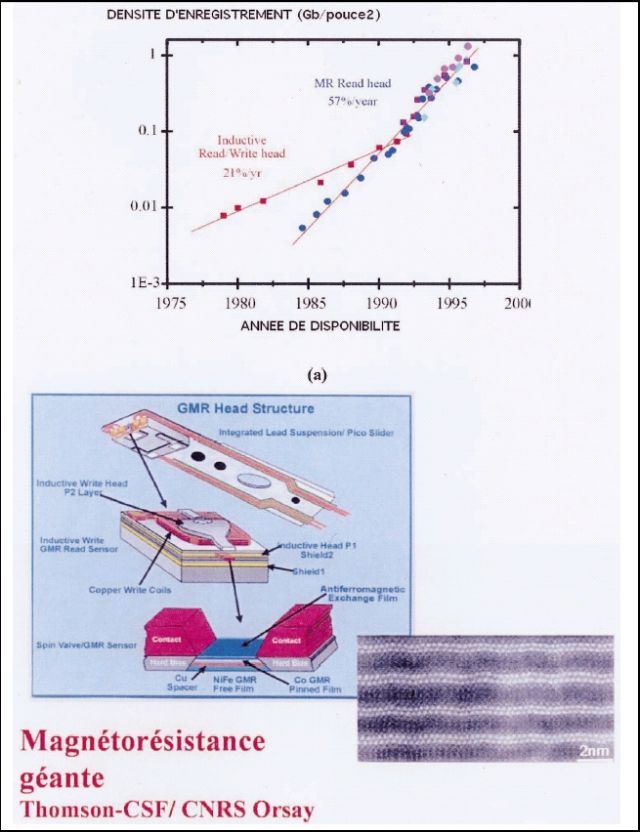

| Fig.17 – La magnétorésistance géante, ŕ la base des tętes de lecture de disques durs modernes, a été découverte en

France (Laboratoire Central de Recherches, Thomson CSF et CNRS, Orsay). Sa mise en œuvre par IBM a abouti ŕ une

accélération remarquable de la densité d’enregistrement des disques durs montrée en (a). Le schéma d’une tęte de

lecture et la photo TEM du matériau sont montrés en (b) (source IBM). retour |

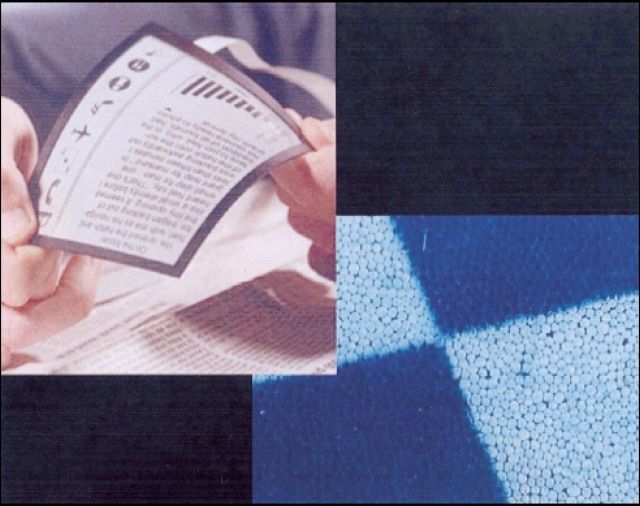

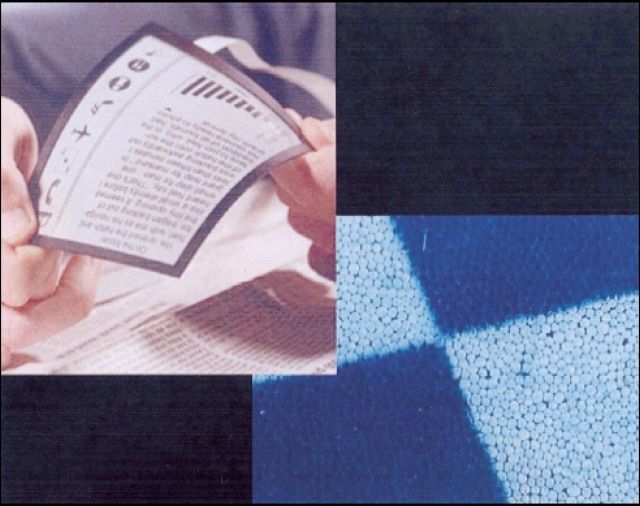

| Fig.18 – Le livre souple ŕ encre électronique devrait trouver un écho favorable dans le

grand public quand il sera commercialisé. Par rapport aux affichages actuels il devrait

conserver l’ergonomie des journaux et livres, tout en ayant une trčs faible consommation :

seule l’inscription d’informations consomme de l’énergie ; l’affichage lui-męme est passif,

grâce ŕ l’éclairage ambiant, dont on a commandé localement l’absorption et la diffusion

(d’oů le nom d’encre électronique). retour |

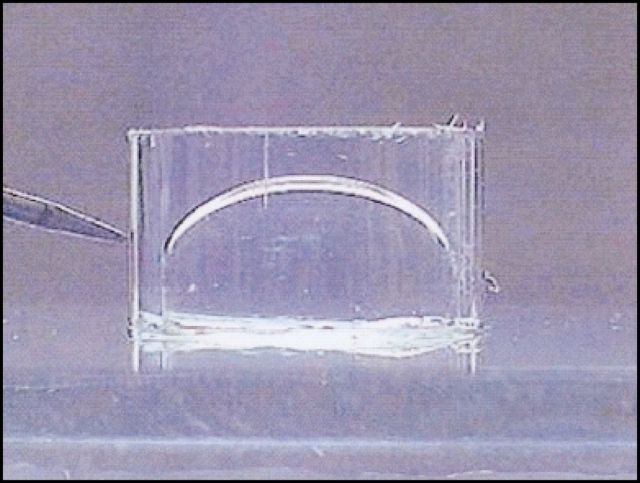

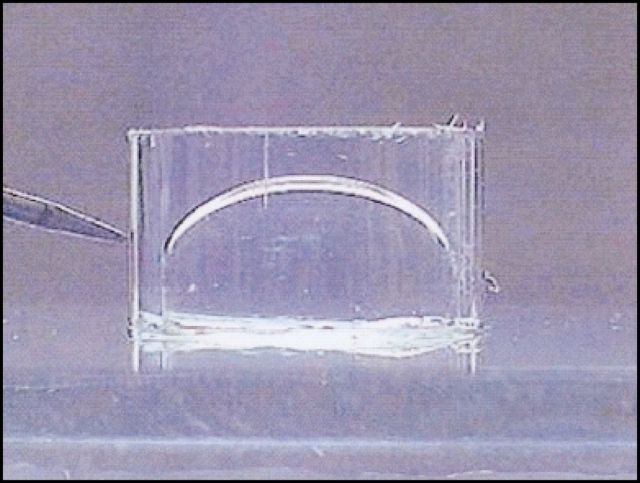

| Fig.19 – La lentille électro-mouillante permet une commande continue

de la courbure de la lentille par application d’un champ électrostatique.

On obtient ainsi une lentille permettant une mise au point commandable

électriquement sans déplacement mécanique. retour |

| Fig.20– Les biopuces sont un champ de recherche particuličrement actif oů la microélectronique, par ses capacités

d’analyse et de transmission d’informations devrait jouer un rôle significatif. L’attrait principal est cependant la miniaturisation

des tests obtenus grâce aux techniques de microfabrication, permettant multiplicité et redondance de diagnostics

effectués en parallčle, en temps réel. retour |

BIBLIOGRAPHIE

1 G.E.Moore, “Cramming more Components onto Integrated

Circuits”, Electronics, 38 (8) (April 19, 1965); reproduit dans

Proc. IEEE, 86, 82 (1998), numéro spécial sur les 50 ans du

transistor ; accessible sur la toile ŕ

http://www.intel.com/research/silicon/mooreslaw.htm

retour

2 Richard Feynman prononça ce discours le 29 décembre 1959

au congrčs annuel de l’American Physical Society au Caltech. Il

fut d’abord publié dans le numéro de février 1960 de la publication

Engineering and Science du Caltech, et reproduit dans H.

D. Gilbert, Miniaturization, Reinhold, 1961, p. 282 (comme illustration

de la miniaturisation ŕ venir). Il est aussi reproduit dans

« Feynman and computation », A. Hey ed., Perseus, 1999.

On peut le trouver sur la toile ŕ

« Feynman and computation » . Pour un historique

(un peu biaisé) de l’impact de cette conférence, voir E.

Regis, "Nano : the emerging science of nanotechnology", Back

Bay, 1991.retour

3 “The Principles of Physics, as far as I can see, do not speak

against the possibility of manoeuvering things atom by atom. It

is not an attempt to violate any laws; it is something, in principle,

that can be done; but in practice, it has not been done because

we are too big”. retour

4 R.W. Keyes, “The cloudy crystal ball: electronic devices for

logic”, Phil. Mag. B, Vol.81, no. 9, pp. 1315-1330 (2001). Voir

aussi R.W. Keyes, The Physics of VLSI systems, Addison

Wesley, 1987; R. Keyes, “Fundamental limits of silicon technology”,

Proc. IEEE, vol.89, pp. 227-239 (2001). retour1 retour2

5 Plus précisément, les quantités qui interviennent sont la transconductance,

g= ≥I/≥V, et le courant ≥I commandé par l’excursion de tension logique ≥V.

C’est ce courant qui va charger la

ligne d’interconnexion de la charge C≥V en un temps C≥V/ ≥I,

soit C/g. On utilise aussi le « fan out » du composant, c’est ŕ dire

la capacité d’un composant ŕ en commander plusieurs autres,

10 par exemple. Le fan out d’un transistor peut ętre infini, mais

alors la vitesse de commande tend vers zéro, puisque la capacité

des transistors qui doivent commuter tend vers l’infini. De

fait, la vitesse des circuits tend ŕ décroître linéairement avec le

fan out mis en oeuvre. C’est ainsi que les circuits logiques les

plus rapides sont les oscillateurs en anneau, avec un fan out de

1, oů une chaîne d’inverseurs ŕ un transistor est mise en auto

oscillation.retour

6 D. Frank et al, "Device scaling of Si MOSFETs and their applications

dependencies", Proc. IEEE, vol. 89, pp. 259-288 (2001). retour

7 La terminologie est un peu délicate ŕ saisir : on parle de nœud

technologique, pour l’ensemble des technologies correspondant

ŕ une génération donnée : 130nm, 90 nm, 65 nm etc. Pour un

nœud, on peut avoir, en męme temps ou décalées dans le

temps, plusieurs tailles pour divers éléments critiques, notamment

la longueur de grille, ce qui améliore nettement la performance

d’une génération donnée sans avoir ŕ remettre en cause

l’ensemble des opérations technologiques pour cette génération.

Enfin, on définit par la lithographie une longueur de grille

"métallurgique", mais la longueur de grille effective, dite "électrique",

celle déterminant la performance, peut ętre assez nettement

plus petite grâce ŕ différentes astuces, ce qui augmente la

performance ŕ finesse de lithographie donnée. Lorsqu’on parle

de technologie la plus avancée ŕ un instant donné, il y a en fait

au moins quatre générations : celle qui est mature, en production

; celle qui est en phase d’industrialisation ; celle qui est en

phase d’intégration des différents éléments de fabrication ;

enfin, celle qui est au niveau de la recherche.retour

8 Voir par exemple J. Davis et al., "Interconnects limits on gigascale

integration in the 21st century", Proc. IEEE, vol. 89, pp. 305324

(2001).retour

9 Ce remarquable document est disponible sur la toile ŕ

http://public.itrs.net/ retour

10 Afin de garder une marge de bruit suffisante, la tension d’alimentation diminue en effet moins vite que les dimensions caractéristiques

du transistor, entraînant une augmentation sensible

des champs électriques (ce qui est bénéfique pour la vitesse,

nuisible pour la fiabilité des transistors) , et mčne bien sűr ŕ une

augmentation de la puissance dissipée par unité de surface.retour

11 Voir par exemple H. C. Lin and S.M. Sze, "Nanoelectronics

technology: in search of the ultimate device structure", dans

"Future trends in microelectronics: the nano, the giga and the

ultra", S Luryi, J. Xu and A. Zaslavsky eds., Wiley, 2004, p.4. retour

12 Voir les 180 composants dans Kwok K. Ng, Complete guide

to semiconductor devices, Mc Graw Hill, 1995.retour

13 A. DeHon, “Array-based architecture for FET-based, nanoscale

electronics”, IEEE Trans. Nanotechnology, vol. 2, 23-32

(2003). M. Butts, A. DeHon and S. Goldstein, “Molecular electronics:

devices, systems and tools for gigagate, gigabit chips”,

Proc ICCAD 2002, pp. 433-440 (2002), disponible sur la toile ŕ

http://www.cs.caltech.edu/research/ic/abstracts/tutorial_iccad20

02.html retour

14 Voir par exemple K. Kim and G. Koh, "Future trends in memory

developments: challenges and perspectives", dans "Future

trends in microelectronics: the nano, the giga and the ultra", S

Luryi, J. Xu and A. Zaslavsky eds., Wiley, 2004, 34.retour

15 P. Avouris et al., "Carbon nanotube electronics", Proc. IEEE, vol. 91,

pp. 1772-1784, 2003.retour

16 H. Goronkin and R.K. Tsui, "Molecular electronics: a proposed

roadmap for commercialization", dans "Future trends in

microelectronics: the nano, the giga and the ultra", S Luryi, J. Xu

and A. Zaslavsky eds., Wiley, 2004, 194.retour

17 S. Laughlin and T. J. Sejnowski, “Communication in Neural

Networks”, Science, vol. 301, pp. 1870-1874 (2003) ; D. Attwell

and S. Laughlin, “An energy budget for signalling in the grey

matter of the brain”, J. of cerebral blood flow and metabolism,

vol. 21, pp. 1133 et suiv. (2001).retour

18 Voir par exemple la discussion de V. Zhirnov et al., "Limits to

binary logic switch scaling: a gedanken experiment", Proc.

IEEE, vol. 91, pp. 1934-1939 (2003).retour

19 J. Meindl, "Low power electronics: retrospect and propect",

Proc. IEEE, vol. 83, pp. 619-635 (1995) ; J. Meindl, Q. Chen and

J. Davis, "Limits on Silicon microelectronics for terascale applications",

Science, vol. 293, pp. 2044-2049 (2001)retour1 retour2

20 Une discussion, męme élémentaire de ce point et de ses

limites (en particulier de savoir s’il s’applique ŕ l’ordinateur

quantique) nous entraînerait trčs loin. Voir les analyses contenues

dans "Maxwell’s demon: entropy, classical and quantum

information, computing", H. Leff and A. Rex eds., Institute of

Physics, 2003.retour

21 Il semblerait qu’il faille plutôt 4.5 nm, somme des distances

de localisation des porteurs dans les régions d’injection et de

collecte (source et drain dans les MOS), et de la barričre de

commande. Ceci est basé sur les énergies de confinement

déduites de l’équation de Schrödinger, et sur le courant tunnel

calculé pour une barričre de largeur et hauteur connue.retour

22 J. M. Lourtioz et al., Les cristaux photoniques, ou la lumičre

en cage, Hermčs, 2003.

Voir aussi, C. Weisbuch et H. Benisty eds., numéro spécial sur

les microcavités et cristaux photoniques, C. R. Acad. Sci. Paris,

t.3, Série IV, pp. 1-102 (2002)retour

23 H. Van Houten,, “The evolution of optical data storage”, in S. Luryi et al. Eds., Fututre trends in

Microelectronics : the nano millenium, Wiley 2002 ; p. 177. retour

24 Voir l’article de synthčse de D. Thompson and J. Best, “The

future of magnetic data storage technology”, IBM J. Res &

Develop., vol. 44, pp. 311 et suiv. (2000), disponible sur la toile.retour

25 P. Vettiger et al., “The millipede – nanotechnology entering

data storage”, IEEE Trans. Nanotechnol., vol. 1, pp. 39 et suiv.

(2002) ; voir aussi P. Vettiger et al., “The millipede: More than

one thousand tips for future AFM data storage”, IBM J. Res. &

Develop., vol. 40, pp. 323 et suiv. (2000), disponible sur la toile.retour

26 B. Comiskey et al., “An electrophoretic ink for all-printed

reflective electronic displays”, Nature, vol. 394, pp. 253 et suiv.

(1998). P. Kazlas and D. McCreary, “Paperlike microencapsulated

electrophoretic materials and displays”, Materials Research

Society Bulletin, November 2002, pp. 894 et suiv.. J. Rogers et

al., “Paper like electronic displays: large area rubber-stamped

plastic sheets of electronics and microencapsulated electrophoretic

inks”, PNAS, vol. 98, pp. 4835 et suiv. (2001). Voir aussi le

trčs fascinant article par J. Jacobson, "The last book", ŕ

http://www.research. ibm.com/journal/sj/363/jacobson.html. retour

27 Robert A. Hayes and B. J. Feenstra, “Video-speed electronic

paper based on electrowetting”, Nature, vol. 425, pp. 383 385

(2003).retour

28 Voir exemple N. Shenck et J. Paradiso, “Energy Scavenging

with Shoe-Mounted Piezoelectrics”, IEEE Micro, May 2001, pp.

30-42. Voir aussi "energy scavenging" sur la toile.retour

29 Voir "smart dust" sur la toile.retour